Microchip expands the choice of 1.6-terabit Ethernet PHYs

Wednesday, February 15, 2023 at 12:40PM

Wednesday, February 15, 2023 at 12:40PM Microchip Technology has enlarged its portfolio of 1.6-terabit physical layer (PHY) Ethernet chips targeting next-generation switch and router line cards.

Stephen Docking

Stephen Docking

In 2021, Microchip announced its PM6200 Meta-DX2L (‘L’ standing for light), its first 1.6-terabit Meta-DX2 PHY that uses 112-gigabit PAM-4 (4-level pulse-amplitude modulation) serialiser/ deserialisers (series).

Microchip has now added four more 1.6-terabit Ethernet PHYs dubbed Meta-DX2+.

Like the Meta-DX2L, the PHYs are implemented using a 6nm CMOS process while the ‘plus’ signifies added features.

The Meta-DX2L is used for such tasks as retiming, for a signal sent across the system’s backplane, for example, and has a ‘gearbox’ feature that translates between 28, 56 and 112-gigabit data rates.

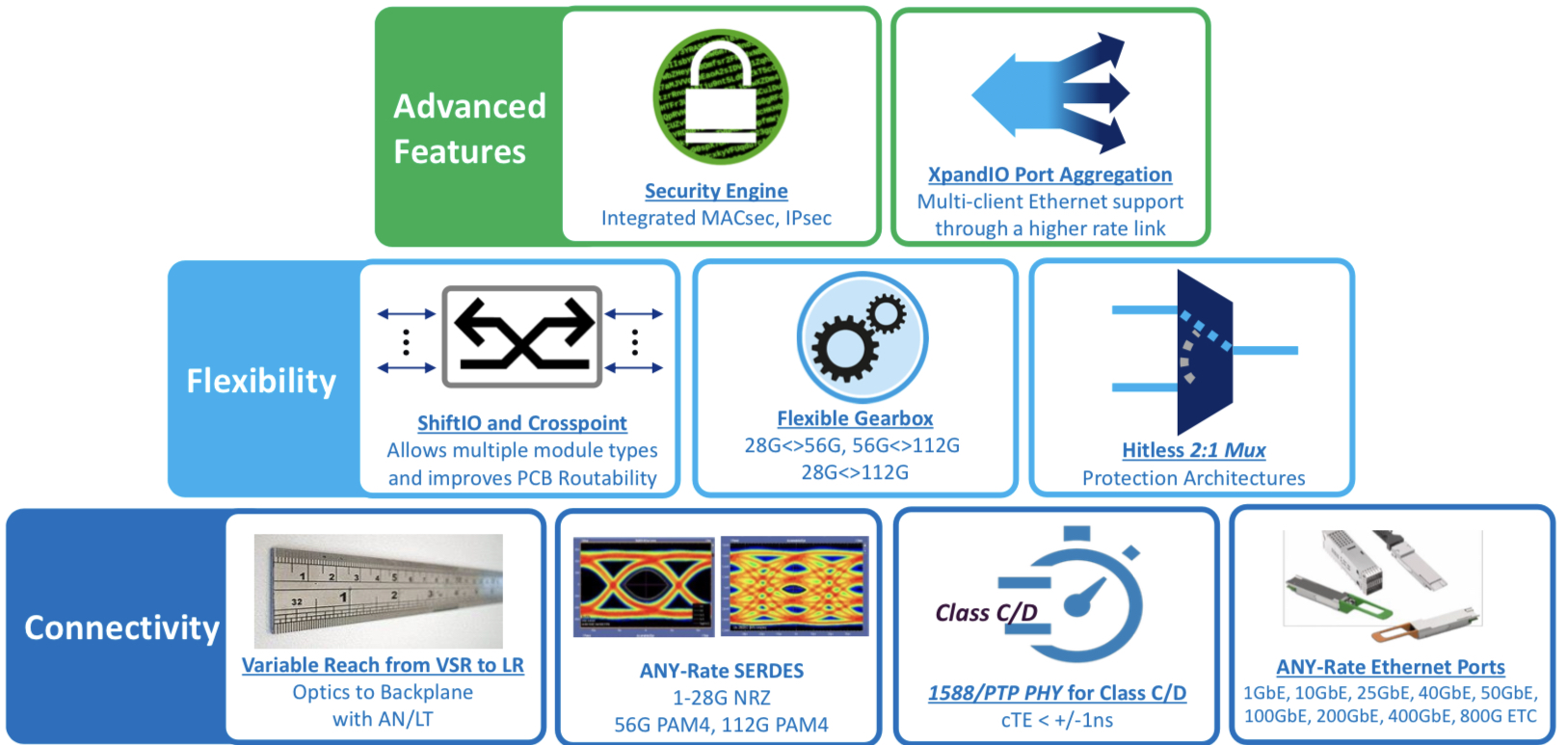

With the Meta-DX2+ PHYs, Microchip has added port aggregation and security hardware.

The Meta-DX2+ ICs adds an extra layer to the pyramid of features. Source: Microchip

The Meta-DX2+ ICs adds an extra layer to the pyramid of features. Source: Microchip

Security and flexibility

Microchip stresses the compact nature of its 1.6-terabit PHYs.

”We see that [compactness] as very important to our customers as they seek to double capacity and design dense systems,” says Stephen Docking, senior manager of product marketing, communications business unit at Microchip.

Security is important for cloud and enterprise, and Microchip claims it has the first PHYs supporting 1.6-terabit of capacity with MACsec and IPsec.

MACsec is used to secure traffic between distributed data centre buildings across a campus or a metropolitan region. IPsec is used for enterprise-wide area networks (WANs) where traffic goes through nodes, some of which may not support encryption.

“The intention is that we can offload those encryption engines having to be in a packet processor or switch device in a system,” says Docking.

The Meta-DX2 1.6-terabit PHYs can interface with 400-gigabit client-side pluggables, emerging 800 gigabit QSFP-DD800s, and upcoming 1.6-terabit OSFP-XD optical modules.

The 1.6 terabit PHYs effectively have two 800-gigabit cores that support rates from 1 to 800 Gigabit Ethernet.

One-gigabit Ethernet is supported as it is still used by enterprises, while 800-gigabit is soon to be deployed, says Docking.

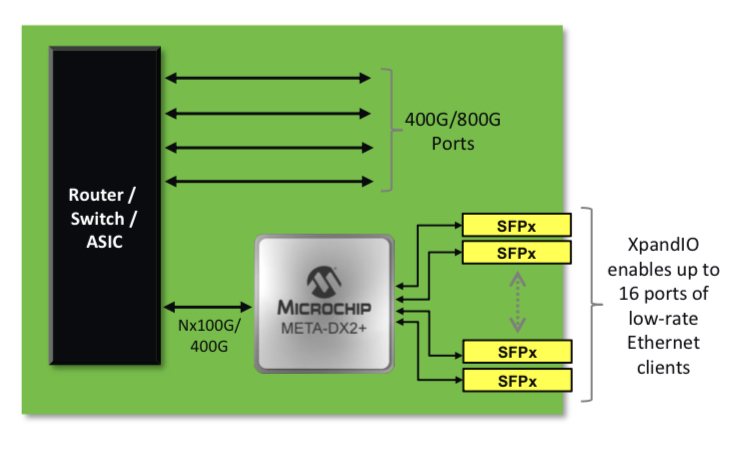

Enterprises also require new switch devices so the 112-gigabit serdes is necessary, but many sub-100 gigabit rates remain in use. Microchip has added its XpandIO feature that aggregates low-speed ports - 1GbE, 10GbE, 25GbE, 50GbE - into the 112-gigabit PAM-4 lane to improve system efficiency.

New packet processor designs have 112-gigabit serdes. If lower rate speeds are fed directly to the packet processor, bandwidth is wasted. Microchip’s XpandIO feature aggregates these lower rates to better match the packet processor’s serdes speed.

XpandIO aggregates lower rates to better match the input traffic to the packet processor’s serdes speed. Source: Microchip

XpandIO aggregates lower rates to better match the input traffic to the packet processor’s serdes speed. Source: Microchip

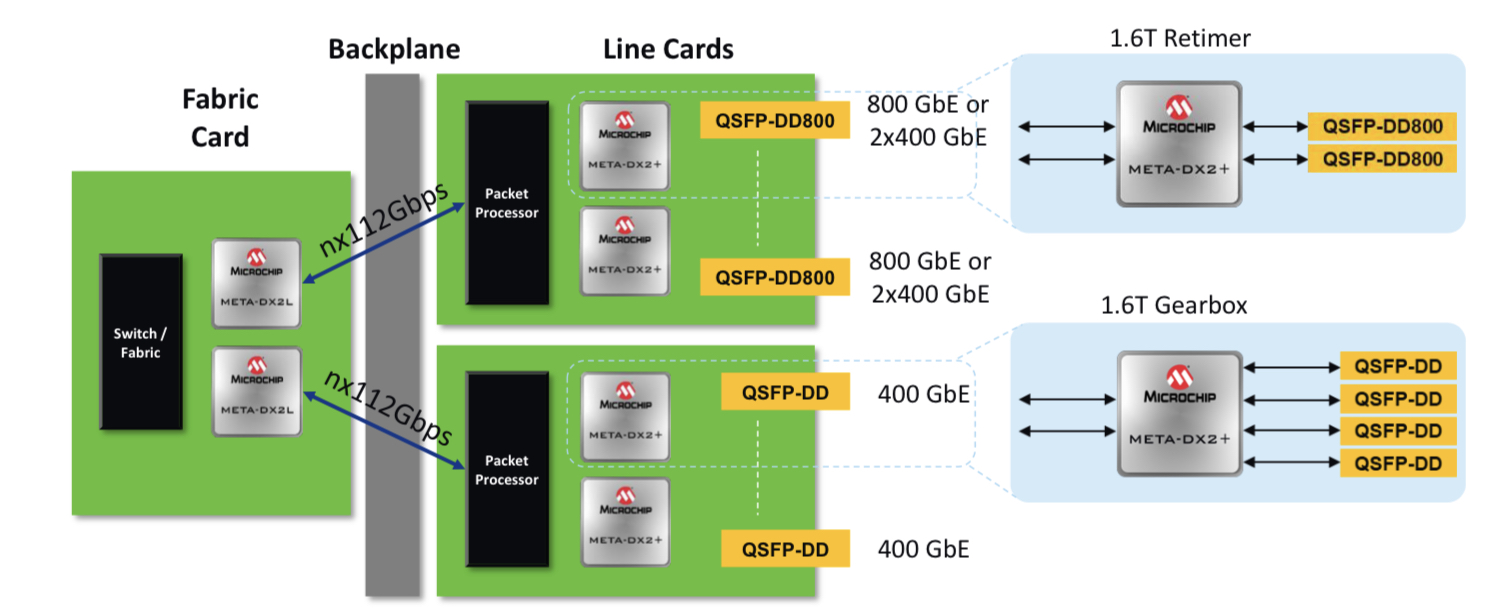

The Meta-DX2+ PHY, like the Meta-DX2L, also feature a hitless 2:1 multiplexer. The multiplexer function is suited for central architecture switch platforms where the system intelligence resides on a central card. In contrast, the connecting line cards are relatively simple, comprising PHYs and optical modules.

In such systems, because of the central role of the platform’s switch card, a standby card is included. If the primary card fails, the backup card kicks in, whereby all the switch’s line cards connect to the backup. The 2:1 multiplexer feature in the PHY means each line card is interfaced with both switch cards: the primary and the backup.

The Meta-DX2 PHY family

The Meta-DX2 PHYs are split into two groupings, the PHYs in each group are hardware compatible such that one line card design is needed.

One group has three PHYs: the PM6200 (the Meta-DX2L), the PM6216 (the Meta-DX2+ PHY with encryption engines), and the PM6210 (a Meta-DX2+ with encryption and XpandIO). All three measure 23x30mm.

The two other Meta-DX2+ PHYs - the PM6214 and the PM6218 (with encryption) - are larger ICs, 33x33mm. This is because the PHYs have 48, 100-gigabit serdes instead of 32 serdes of the first group.

The extra 16 100-gigabit serdes enable the PHYs to support, for example, 16 100-gigabit lanes (1.6-terabit) when connected to a switch IC as well as 32 lanes of 50-gigabit serdes used in 8x50-gigabit 400-gigabit QSFP-DD modules.

“The PHY package size, in this case, is larger,” says Docking. “But even with that, we still have a net 20 per cent reduction in total area.” That can make a difference between fitting in a one rack unit (1RU) design rather than 2RU.

All PHYs share a common software development kit. The software kit also supports the switch abstraction interface standard. “This decouples the operating systems from the underlying hardware,” says Dorking.

The Meta-DX2+ PHYs have been sampling since the final quarter of 2022 and the chips are available for prototypes.

Applications

The PHY portfolio caters for several classes of system designs. Microchip cites cloud and enterprise data centre switches and routers, service provider routers, encryption boxes, and optical transport platforms.

A router/ switch line card showing how the Meta-DX2 PHYs can be used on fabric cards and line cards for different tasks such as retiming and gearbox modes. Source: Microchip

A router/ switch line card showing how the Meta-DX2 PHYs can be used on fabric cards and line cards for different tasks such as retiming and gearbox modes. Source: Microchip

Microchip says that the Meta-DX2L was released to address the first generation of higher capacity line cards where retiming and gearbox rate changes are essential.

The remaining 1.6-terabit PHYs available now better address system vendors’ second-generation card designs that typically add features such as encryption.

What next?

A next obvious PHY family will be when the 224-gigabit electrical interface becomes available.

Kevin So

Microchip says it has invested more in this generation of 112-gigabit series-based PHYs than previous generations and it expects 112-gigabit serdes to be more of a ‘workhorse’ than in the past.

“I think what you will find is more 112-gigabit based solutions rather than every new investment cycle being a new line rate,” says Kevin So, director, product line management and marketing, communications business unit at Microchip.

It will not be the cadence of investments that changes, rather those investments will likely be anchored around the 112-gigabit electrical interface.

Reader Comments