PCI-SIG targets 256GT/s with the PCIe 8.0 bus protocol

Thursday, October 23, 2025 at 10:50AM

Thursday, October 23, 2025 at 10:50AM Next-generation PCIe doubles lane speed again, but design challenges mount as AI reshapes interconnect needs.

The Peripheral Component Interconnect Special Interest Group (PCI-SIG), a 1,000-plus-member organisation that oversees the specification work of the long-established PCI Express (PCIe) bus used across industries, is progressing to specify the next version of the standard.

Source: PCI-SIG

Source: PCI-SIG

Dubbed PCIe 8.0, the newest standard will double the bus's speed per lane to 256 giga-transfers per second (GT/s), twice the transfer rate of the PCIe 7.0 standard ratified in June. First PCIe 7.0-based products are expected next year.

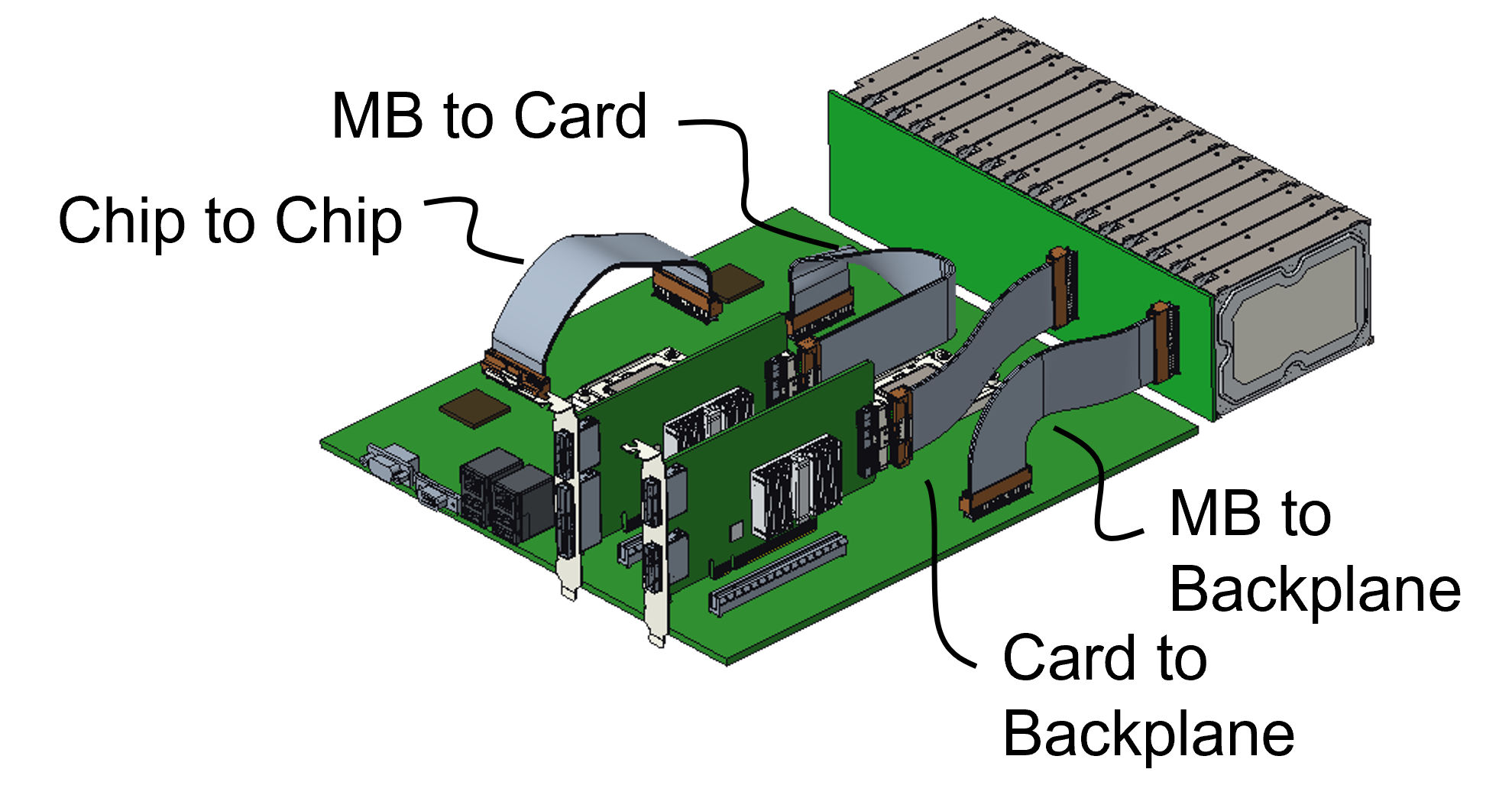

In the data centre, PCIe is used by general-purpose processors in servers and AI accelerator clusters, connecting processors to storage and network interface cards (see chart above).

Al Yanes,

Al Yanes,  Bob Wheeler,

Bob Wheeler,  OpenAI,

OpenAI,  PCI-SIG,

PCI-SIG,  PCIe 7.0,

PCIe 7.0,  PCIe 8.0 in

PCIe 8.0 in  artificial intelligence

artificial intelligence  Print Article

Print Article