ADVA and II-VI’s coherent partnership

Tuesday, June 21, 2022 at 5:53AM

Tuesday, June 21, 2022 at 5:53AM - ADVA and II-VI have jointly developed a 100-gigabit coherent DSP

- Both companies plan to use the 2.0-2.5W, 7nm CMOS Steelerton DSP for a 100ZR QSFP28 module

- II-VI’s ASIC design team engineered the DSP while ADVA developed the silicon photonics-based optics.

ADVA and II-VI have joined forces to define a tiny coherent digital signal processor (DSP) that fits inside a QSFP28 optical module.

Christoph Glingener

Christoph Glingener

The Steelerton DSP can send a 100-gigabit dense wavelength-division multiplexing (DWDM) transmission over 80-120km, carrying wireless backhaul and access traffic.

“It is backhaul of broadband, it is backhaul of mobile, and it definitely moves outdoors,” says Christoph Glingener, CTO at ADVA.

The module also serves metro networks with its 300km reach using optical amplification.

II-VI and ADVA now join such established coherent players as Ciena, Huawei, Infinera, Nokia as well as Marvell, NEL, and Acacia, now part of Cisco.

Effect Photonics announced at OFC earlier this year its coherent market entry with its acquisition of the Viasat DSP team.

Motivation

ADVA says it entered the coherent DSP market after failing to find a design suited for backhaul, a coherent market that promises highest unit volumes.

Backhaul has become even more important market for ADVA given its merger with broadband equipment maker ADTRAN.

II-VI also notes how access rates are moving from 10 to 100 gigabits.

“We were looking to develop a DSP capable to target a market that is underserved and where we can differentiate. This analysis led us to the 100ZR with a purpose-built DSP solution” says John DeMott, vice president product management, coherent and tunable product lines at II-VI.

John DeMott

John DeMott

The 100-gigabit coherent market for access contrasts with 400-gigabit coherent that uses modules such as 400ZR and 400ZR+ to connect data centres.

ADVA did consider existing suppliers’ coherent DSPs but deemed them too big and power-hungry for this application. This is what led to the II-VI partnership.

“We found a partner in II-VI that was willing to do this, but to get to the required power envelopes, we needed a 7nm DSP,” says Glingener. “And 7nm CMOS technology is not cheap.“

II-VI has a staff of mixed-signal and ASIC engineers in Germany that designed the Steelerton chip.

The two firms now have their own 100-gigabit DSP and can start developing coherent product roadmaps.

Applications

The 100ZR module will be deployed at aggregation sites.

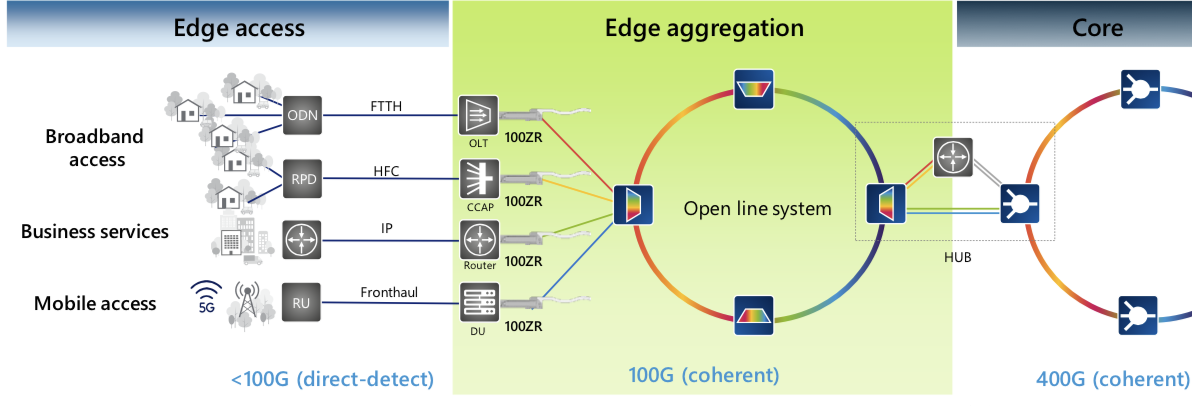

ADVA shows how the 100ZR module is used for edge aggregation (see diagram).

Source: ADVA

Source: ADVA

Another application is 100-gigabit data-centre interconnect (DCI) for enterprises; hyperscalers require 400 gigabit and higher rates for DCI.

II-VI says the DSP is suited for access and metro applications. The 100ZR module fits a wavelength in a 50GHz channel to enable 96 DWDM wavelengths across the C-band. The 100ZR module has a maximum reach of 300km when used with amplification.

“The 22dB loss budget supports up to 80km without in-line amplification and up to 300km with in-line amplification, limited by chromatic dispersion,” says DeMott.

II-VI highlights several use-cases for the 100ZR module.

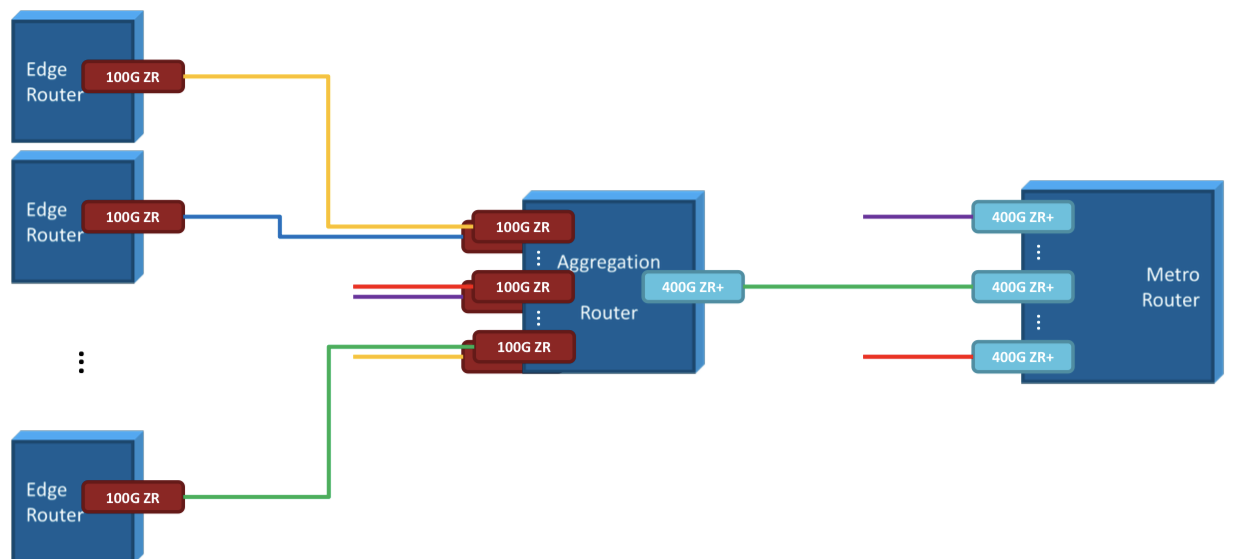

One is IP-over-DWDM, connecting edge routers to an aggregation router (see diagram) or a muxponder. The aggregated 100-gigabit wavelengths are sent to a metro router using a 400-gigabit 400ZR+ coherent module. II-VI also has 400ZR+ modules.

Source: II-VI

Source: II-VI

Two factors dictate the 100ZR module design: power consumption and the form factor.

Even a module power consumption of 10W is too high for access. Also, the DSP and optics must fit inside a QSFP28 since this is a common form factor for access equipment uplinks.

The resulting DSP has a power consumption of 2.0-2.5W and the chip is a fifth the size of other 7nm coherent DSPs. The 100ZR QSFP28 module - the DSP and optics - consumes 5.0-5.5W.

The DSP is stripped down to its essential features to achieve the power target. For example, the DSP uses one modulation format only: dual-polarisation, quadrature phase-shift keying (DP-QPSK).

“You de-feature the DSP down to a level that you can meet the power envelope, and it is not that complicated anymore,” says Glingener.

ADVA developed the silicon photonics analogue front end for the module that uses a single laser. To fit the DSP and the optics in a QSFP28 also proved an integration challenge.

The Steelerton DSP is taped out and both companies expect to have 100ZR prototype modules in the second half of this year.

What next

ADVA is planning a 100ZR+ module that will have enhanced optical performance that will be available in prototype form in early 2023.

ADVA’s coherent module interest remains broadband. Possible developments include a 5nm CMOS 200-gigabit DSP or a cheaper, more power-efficient, second-generation 100-gigabit design.

ADVA is also exploring concepts such as a parallel design, a 4x100G implementation.

Meanwhile, II-VI is looking at high-end coherent designs, which may include multiple sources for silicon photonics

“The next obvious steps are 800 gigabits and 1.6 terabits,” says DeMott. “There is a lot of [industry] activity, so those would be directions we're considering.” II-VI has in-house optics for high-end coherent designs.

There will be a market for 800-gigabit coherent modules, says DeMott, but hyperscalers already are asking for 1.6-terabit designs.

“These are divergent DSPs,” says DeMott. “You can't do a DSP that does 1.6 terabits, 800 gigabits and 400 gigabits; it's either a 1.6-terabit or a 400/ 800-gigabit DSP design.”

Reader Comments