DT chooses Nokia for a major optical network upgrade

Thursday, February 18, 2021 at 10:31AM

Thursday, February 18, 2021 at 10:31AM Deutsche Telekom is redesigning its domestic optical network and has chosen Nokia as its equipment supplier.

“They are re-architecting and rolling out, in a short time, a huge portion of their optical network,” says Kyle Hollasch, (pictured) director of optical portfolio marketing, Nokia. “We are displacing in many parts of the network four different vendors.”

Network architecture

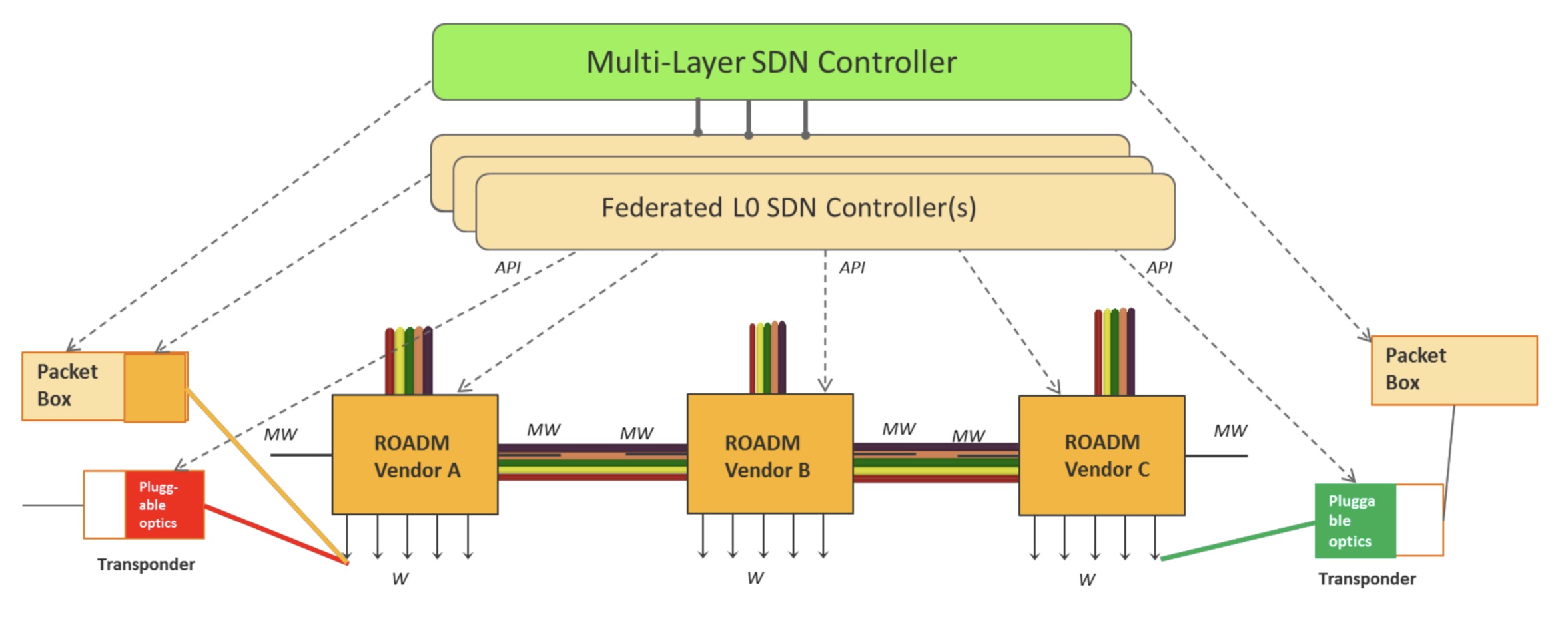

Deutsche Telekom’s legacy mesh-based wavelength-division multiplexing (WDM) network uses equipment from several vendors. In the last decade, Deutsche Telekom also added to the core an IP-optical solution from Cisco Systems.

Now, the CSP is replacing the mesh-WDM network and the Cisco IP-optical core with an OTN-WDM core from Nokia.

“They are unifying their traffic from all of their business services, government services, 5G anyhaul and the core IP network onto one core WDM network,” says Hollasch.