Increasing the baud rate of coherent modems benefits optical transport. The higher the baud rate the more data can be sent on a wavelength, reducing the cost-per-bit of traffic.

But engineers have become so good at designing coherent systems that they are now approaching the Shannon limit.

Tomislav Drenski

Tomislav Drenski

At the OFC show earlier this year, Ciena showcased a coherent module operating at 107 gigabaud (GBd). And last year, Acacia, now part of Cisco, announced its next-generation 1.2 terabits-per-second (Tbps) wavelength coherent module operating at up to 140GBd.

The industry believes that increasing the baud rate to 240+GBd is possible, but each new symbol-rate hike is challenging.

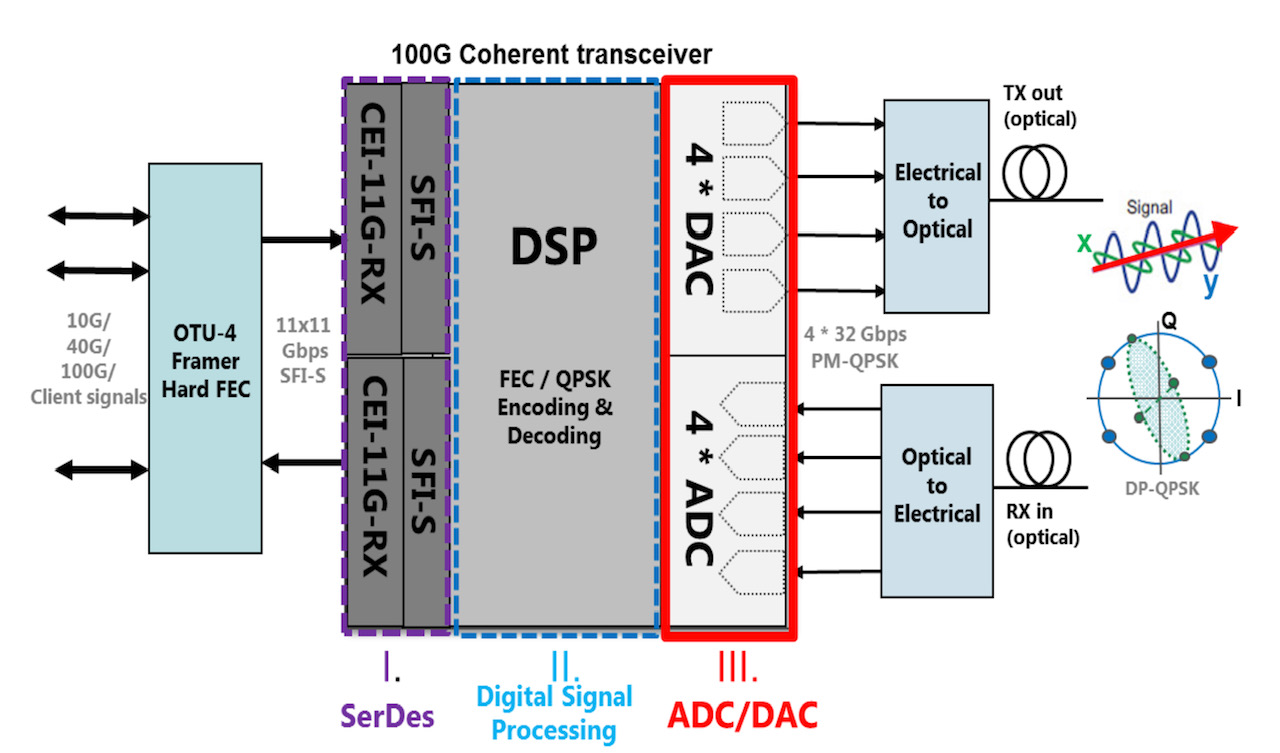

All the components in a modem - the coherent DSP and its digital-to-analogue (DAC) and analogue-to-digital (ADC) converters, the optics, and the analogue drive circuitry - must scale in lockstep.

Gigabaud and giga-samples

Coherent DSPs continue to improve in optical performance with each new CMOS process. The latest DSPs will use 5nm CMOS, while the semiconductor industry is developing 3nm CMOS and beyond.

Optical device performance is also scaling. For example, a 220GBd thin-film lithium niobate modulator has been demonstrated in the lab, while photodetectors will also achieve similar rates.

However, the biggest challenge facing coherent modem engineers is the analogue drive circuitry and the coherent DSP’s ADCs and DACs.

A key performance metric is its sampling rate measured in giga-samples-per-second (Gsps).

Coherent DSP showing the ADCs and DACs. Source: Socionext

Coherent DSP showing the ADCs and DACs. Source: Socionext

According to Nyquist, a signal needs to be sampled at twice its baud rate to be perfectly reconstructed. But that doesn't mean sampling is always done at twice the baud rate. Instead, depending on the DSP implementation, the sampling rate is typically 1.2-1.6x the symbol rate.

“So, for a 200 gigabaud coherent modem, the DSP's converters must operate at 240+ giga-samples per second,” says Tomislav Drenski, marketing manager, wireline, at Socionext Europe.

Socionext

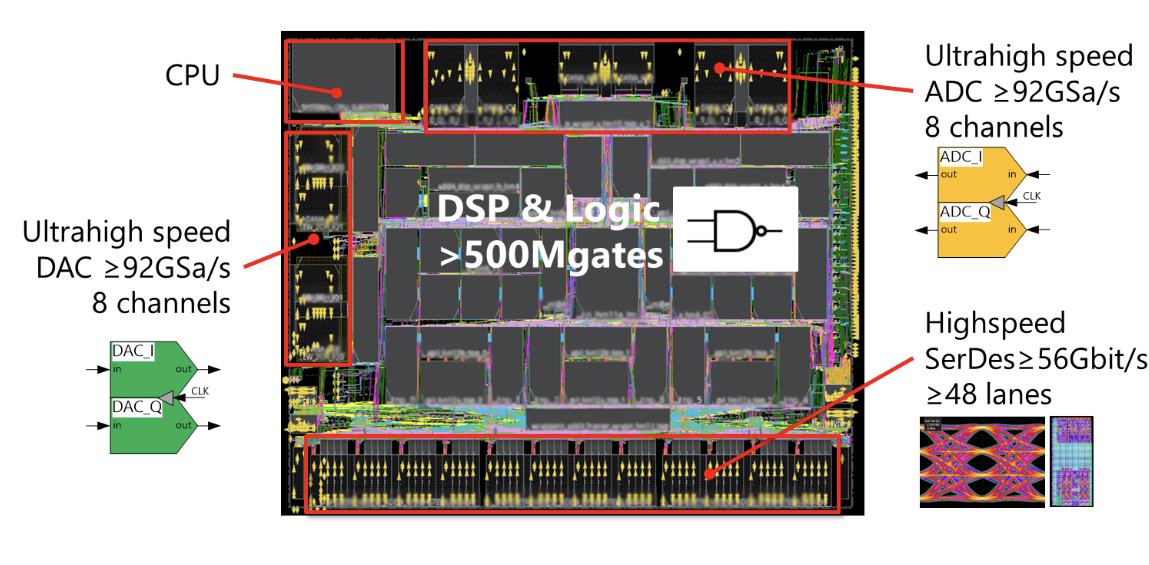

Socionext is a system-on-chip specialist founded in 2015 with the combination of the system LSI divisions of Fujitsu and Panasonic, with its headquarters in Japan. Its European arm focuses on mixed-signal design, especially ADC, DACs and serialisers/ deserialisers (Serdes).

The company has developed 8-bit converters for several generations of long-haul optical designs, at 200Gbps, 400Gbps and greater than 1Tbps (see bottom photo). These optical systems used ADCs and DACs operating at 65, 92 and 128Gsps, respectively.

Socionext works with leading coherent optical module and network system providers but is also providing 5G and wireless ASIC solutions.

"We design the ADCs and DACs, which are ultra-high-speed, state-of-the-art circuit blocks, while our partners have their ideas on how the DSP should look," says Drenski. "They provide us the DSP block, and we integrate everything into one chip."

It is not just the quality of the circuit block that matters but how the design is packaged, says Drenski: “If the crosstalk or the losses in the package are too high, then whatever you have got with the IP is lost in the packaging.”

Any package-induced loss or added capacitance decreases bandwidth. And bandwidth, like sampling rate, is key to achieving high baud-rate coherent systems.

Design considerations

An important ADC metric is its resolution: the number of bits it uses to sample a signal. For high-performance coherent designs, 8-bit ADCs are used. However, because of the high sampling rate required and the associated jitter performance, the effective number of bits (ENOB) - an ADC metric - reduces to some 6 bits.

"People are asking for 10-bit converters for newer generations of design; these are shorter reach, not ultra-long-haul," says Drenski.

Extra bits add fidelity and enable the recovery of higher-order modulated signals. Still, for ultra-long-haul, where the optical loss is more significant, using a 10-bit ADC makes little sense.

For 5G and wireless applications, higher resolutions, even going up to 14bit, is the recent trend. But such solutions use a lower sampling rate - 30Gsps - to enable the latest, direct-RF applications.

1Tbps ASIC implementation example. Source: Socionext

1Tbps ASIC implementation example. Source: Socionext

ADC architecture

An interleaved architecture enables an 8-bit ADC to sample a signal 128 billion times a second.

At the input to the ADC sits a sample-and-hold circuit. This circuit feeds a hierarchy of interleaved 'sub-ADCs'. The interleaving goes from 1 to 4, then 4 to 16, 16 to 64, with the sub-ADCs all multiplexed.

"You take the signal and sample-and-hold it, then push everything down to many sub-ADCs to have the necessary speed at the end, at the output," says Drenski.

These sub-ADCs must be aligned, and that requires calibration.

An ADC has three key metrics: sampling rate, bandwidth and ENOB. All three are interdependent.

For example, if you have a higher bandwidth, you will have a higher frequency, and clock jitter becomes a limiting factor for ENOB. Therefore, the number of sub-ADCs used must be well balanced and optimised to realise the high sampling frequencies needed without affecting ENOB. The challenge for the designer is keeping the gain, bias and timing variations to a minimum.

Drenski says designing the ADC is more challenging than the DAC, but both share common challenges such as clock jitter and also matching the path lengths of the sub-DACs.

240 gigabaud coherent systems

Can the bandwidth of the ADC reach 240+GBd?

"It all comes down to how much power you can spend," says Drenski. "The more power you can spend to linearise, equalise, or optimise, the better."

Noise is another factor. The amount of noise allowed determines how far the bandwidth can be increased. And with higher bandwidth, there is a need for higher clock speeds. "If we have higher clock speeds, we have higher complexity, so everything gets more complicated," says Drenski.

The challenges don't stop there.

Higher sampling rates mean the number of sub-ADCs must be increased, affecting circuit size and power consumption. And limiting the power consumption of the coherent DSP is a constant challenge.

At some point, the physical limitations of the process - the parasitics - limit bandwidth, independent of how the ADC circuitry is designed.

Coherent optics specialists like Acacia, Nokia, ADVA and Lumentum say that 220-240 gigabaud coherent systems are possible and will be achieved before the decade’s end.

Drenski agrees but stresses just how challenging this will be.

For him, such high baud rate coherent systems will only be possible if the electronics and optics are tightly co-integrated. Upping the bandwidth of each essential element of the coherent system, like the coherent DSP's ADCs and DACs, is necessary but will not work alone.

What is needed is bringing both worlds together, the electronics and the optics.